# **Data Sheet**

Type Description: Green-Mode PWM Flyback

(SSR) Controller

Product Name: EST.30xxM

Reversion: V1.0

Reversion Date: May, 2020

Page: 16 Pages

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### **General Description**

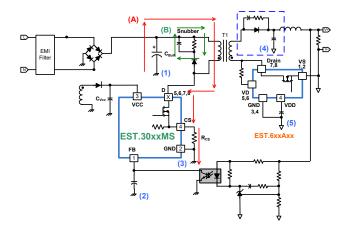

EST.30xxM is a higher integrated PWM flyback controller. It provides several functions to enhance the efficiency to meets the criteria of global standards such as DoE Level VI and EU CoC V5 Tier-2. Meantime, it also provides excellent EMI-improved solution, and also built in complete protection.

EST.30xxM is a green mode controller, which implements low start-up current, green-mode power-saving. It is also built-in the leading-edge blanking (LEB) of the current sensing and feedback loop to screen the spike noise from any input signal. The internal slope compensation can limit the constant output over universal AC input range. The sawtooth over frequency function for EMI improved solution.

Meanwhile, EST.30xxM also provides various protection, such as, OLP (Over Load Protection), VDD OVP (Over Voltage Protection), Output OLP and output OVP to prevent the circuit damage from the abnormal conditions.

EST.30xxM is available in DIP-7.

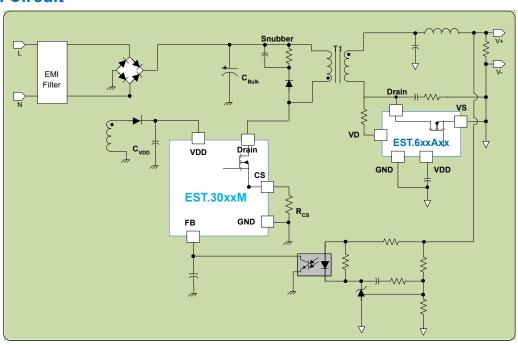

EST.30xxM works with current sensing synchronous rectifier controllers, such as EST.6002A or EST.6xxAxxC to achieve higher conversion efficiency and very compact power density.

# **Application**

- Switching AC/DC adapter and battery charger

- ATX standby power

- Open frame switching power and CD(R)

- Set-top-boxes(STB) 384Xreplacement

#### **Features**

- Integrated650V/ 700V Start-Up Device and MOSFET

- 100KHz fix frequency mode at PWM Mode

- Very low startup current (<3 uA)</li>

- Soft Driving for Reducing EMI Noise

- ◆ 0.5mA ultra-low operating current at light load

- Current mode control with Cycle-by-Cycle current limit

- Built-in slope and load regulation compensation

- LEB (Leading-edge blanking) on CS Pin

- UVLO (Under voltage lockout)

- Fault Protections: VDD Over Voltage, Output Short-Circuit, Over-Current, OLP (Over load protection) and Pin Fault

- Photo coupler short protection & Feedback open protection

- High voltage CMOS process with excellent ESD protection

- ◆ 250mA/-500mA driving capability

- Hazardous Substance Free

- ◆ RoHs/REACH Compliant

### **Function and Protection Options**

| Part      | Dankana | Freq.  | req. Protection                         |        |        |        |        |  |  |  |  |  |  |

|-----------|---------|--------|-----------------------------------------|--------|--------|--------|--------|--|--|--|--|--|--|

| No.       | Package | KHZ    | VCC OVP OLP(65mS) CS Open SDSP Line OVP |        |        |        |        |  |  |  |  |  |  |

| EST.30xxM | DIP-7L  | 100KHz | Hiccup                                  | Hiccup | Hiccup | Hiccup | Hiccup |  |  |  |  |  |  |

Note: EST lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. EST lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for MSL classification at lead-free peak reflow temperature. EST defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight)

# **Ordering Information**

| Part Number | Package | Packaging | Note  |

|-------------|---------|-----------|-------|

| EST.30xxM   | DIP-7L  | Tape      | Green |

EST: LOGO

YY: Year code

WW: Week code

30xxM: xx= MOS Type

XXXX: Production lot code

| DIP-7 | NAME Description | Description                                             |

|-------|------------------|---------------------------------------------------------|

| 1     | CS               | Current Sense pin, connect to sense the MOSFET current. |

| 2     | NC               |                                                         |

| 3     | GND              | Ground                                                  |

| 4     | FB               | Voltage input pin by connecting a photo-coupler         |

| 5     | VDD              | Power supply pin                                        |

| 6,7   | Drain            | For start-up, the pin is also HV power MOSFET drain pin |

# **Application Circuit**

### **Absolute Maximum Ratings**

| Developator Comphal                              | Parameter Symbol |                           |      | Values           | l lmit | Damanis |

|--------------------------------------------------|------------------|---------------------------|------|------------------|--------|---------|

| Parameter Symbol                                 |                  | Symbol                    | Min. | Max              | Unit   | Remark  |

| Supply Voltage VDD                               |                  | $V_{DD}$                  | -0.3 | 32               | V      |         |

| FB,CS Voltage                                    |                  | $V_{AC}, V_{FB}, V_{CS},$ | -0.3 | 7                | V      |         |

| Drain Voltage                                    |                  | $V_D$                     | 700  |                  | V      |         |

| Max Junction Temperature                         |                  | $T_{im}$                  | -40  | 150              | °C     |         |

| Operation Junction Temperature                   |                  | Tj                        | -40  | 125              | °C     |         |

| Operation Ambient Temperature                    |                  | TA                        | -25  | 85               | °C     |         |

| Storage Temperature                              |                  | T <sub>stg</sub>          | -55  | 150              | °C     |         |

| Absolute Max. IDD Current @ V <sub>DD</sub> =25V |                  | I <sub>DD_max</sub>       | -    | 22               | mA     |         |

| Power Dissipation                                | Ta = 25℃         | PD                        | -    | 1100             | mW     | DID 7   |

| Junction-to-Ambient Thermal Resistance*          |                  | $\theta_{JA}$             | -    | 85 <sup>*2</sup> | °C/W   | DIP-7   |

| Junction-to-Case Thermal Resistance**            |                  | θ <sub>JC</sub>           | -    | 20 <sup>*3</sup> | °C/W   |         |

| Lead temperature (Soldering, 10 sec)             |                  |                           | -    | 260              | °C     |         |

| ESD Voltage Protection                           | HBM              | V <sub>ESD-HBM</sub>      | -    | 3.0              | KV     |         |

| ESD Voltage Protection                           | MM               | V <sub>ESD-MM</sub>       | -    | 300              | V      |         |

\*1All items are tested with the standards JESD 51-2 and 51-10(DIP).

Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliablity.

\*2. Free standing with no heatsink; without copper clad (Measeurment condition: just before junction temperature Tj, enters into OTP)

\*3.Measure on the DRAIN pin close to plastic interface

#### **Recommended Operating Conditions**

| Parameter Symbol          | Symbol            | Limit | Values | Unit  | Remarks |

|---------------------------|-------------------|-------|--------|-------|---------|

| Parameter Symbol          | Symbol            | Min.  | Max    | Offic | Remarks |

| Supply Voltage VDD        | VDD               | 11    | 25     | V     |         |

| Startup Resistor Value    | R <sub>star</sub> | 1     | 14     | МΩ    |         |

| Ambient temperature range | T <sub>opr</sub>  | -40   | 85     | °C    |         |

| Capacitance of FB pin     | C <sub>FB</sub>   |       | 2.2    | nF    |         |

| Capacitance of CS pin     | C <sub>CS</sub>   | 47    | 390    | pF    |         |

#### DC Electrical Characteristics (VCC =15V, Ta=25°C)

#### Supply Voltage (VDD Pin):

| Parameter                                       | Symbol                  | Min. | Тур. | Max. | Unit  | Conditions                   |

|-------------------------------------------------|-------------------------|------|------|------|-------|------------------------------|

| Startup Current                                 | I <sub>DD-ST</sub>      |      | 2    | 3    | μА    | VDD=15V                      |

| On a rational Command                           | I <sub>DD-OP</sub>      | 0.4  | 0.6  | 0.8  | mA    | V <sub>FB</sub> =0V          |

| Operating Current<br>(with 1nF load on DRV pin) | I <sub>DD-OP</sub>      | 1    | 2    | 2.3  | mA    | V <sub>FB</sub> =2.5V CL=1nF |

| (with the load on bity pin)                     | I <sub>DD-OLP</sub>     | 0.2  | 0.35 | 0.5  | mA    | Protection Current           |

| UVLO (off)                                      | V <sub>UVLO-OFF</sub>   | 7.5  | 8    | 8.5  | V     |                              |

| UVLO (on)                                       | V <sub>UVLO-ON</sub>    | 16   |      | 19   | V     |                              |

| VDD OVP Level                                   | V <sub>OVP</sub>        | 26   | 27   | 28.5 | V     |                              |

| OVP Debounce Time                               | T <sub>OVP</sub>        |      | 4    |      | cycle | Guarantee by Design          |

| VDD Simulation mode(ON)                         | $V_{DD-HD\_ON}$         | 9.7  |      | 10.7 | V     |                              |

| VDD Simulation mode(OFF)                        | $V_{DD\text{-}HD\_OFF}$ | 10.2 |      | 11.2 | V     |                              |

| Latch off mode release Current                  | IDD <sub>-LHOFF</sub>   |      |      | 25   | uA    | Guarantee by Design          |

#### Voltage Feedback(FB Pin):

| Tollago Foodback(FB Fill)    |                     |      |      |      |      |                       |

|------------------------------|---------------------|------|------|------|------|-----------------------|

| Parameter                    | Symbol              | Min. | Тур. | Max. | Unit | Conditions            |

| Short Circuit Current        | I <sub>Zero</sub>   | 0.1  | 0.14 | 0.18 | mA   | V <sub>FB</sub> =0V   |

| Open Loop Voltage            | V <sub>FB-OP</sub>  | 4.8  | 5    | 5.2  | V    | FB pin open           |

| Over Load Protection         | V <sub>OLP</sub>    | 3.5  | 4    | 4.5  | V    |                       |

| Debounce Time of OLP         | T <sub>OLP</sub>    | 55   | 65   | 75   | ms   |                       |

| Burst mode start voltage(on) | V <sub>BUR_ON</sub> | 0.35 | 0.45 | 0.55 | V    |                       |

| Burst Mode Hysterics         | V <sub>BUR_HY</sub> | 0.05 | 0.1  | 0.15 | V    |                       |

| Green Mode Threshold         | F <sub>th_GR</sub>  | 55   | 60   | 75   | KHz  | V <sub>FB</sub> =1.3V |

Current Sensing (CS Pin):

| Parameter                                                   | Symbol                            | Min. | Тур. | Max. | Unit  | Conditions           |

|-------------------------------------------------------------|-----------------------------------|------|------|------|-------|----------------------|

| Leading Edge Blanking Time &<br>Propagation Delay to Output | T <sub>LEB</sub> +T <sub>PD</sub> | 400  | 500  | 600  | ns    |                      |

| Maximum CS Off Voltage                                      | V <sub>CSTH</sub>                 | 0.65 | 0.7  | 0.75 | V     |                      |

| OCP source current                                          | I <sub>OCP</sub>                  | 240  | 250  | 260  | uA    | Min. Duty            |

| CS Over Voltage Protection                                  | V <sub>CS_OVP</sub>               | 0.45 | 0.5  | 0.55 | V     | $T = T_{\text{off}}$ |

| OVP Leading Blanking time                                   | T <sub>OVP_LEB</sub>              |      | 2    |      | us    |                      |

| Internal Slope Compensation                                 | V <sub>SLP_LP_LEB</sub>           |      | 160  |      | mV    |                      |

| Short Circuit Protection Voltage                            | V <sub>SCP</sub>                  |      | 1    |      | us    | Guarantee by Design  |

| Debounce Time of V <sub>SCP</sub>                           | T <sub>SCP</sub>                  |      | 4    |      | cycle |                      |

| Short Circuit Detection Time                                | T <sub>SCP</sub>                  |      | 100  |      | us    |                      |

Alternating Current Detect(AC Pin):

| Parameter               | Symbol           | Min. | Тур. | Max. | Unit | Conditions |

|-------------------------|------------------|------|------|------|------|------------|

| Brown In trigger point  | $V_{BNI}$        | 0.8  | 0.85 | 0.9  | V    |            |

| Brown Out trigger point | V <sub>BNO</sub> | 0.65 | 0.7  | 0.75 | V    |            |

| BNO De-bounce time      | T <sub>BNO</sub> | 20   | 26.5 | 30   | ms   |            |

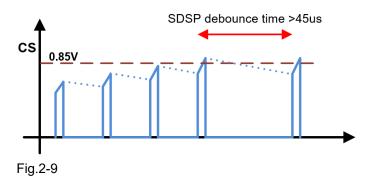

SDSP (Secondary diodes short protection):

| Parameter         | Symbol               | Min. | Тур. | Max. | Unit  | Conditions          |

|-------------------|----------------------|------|------|------|-------|---------------------|

| SDSP CS pin level | V <sub>CS_SDSP</sub> |      | 0.85 |      | V     |                     |

| De-bounce Cycle   | TD_SDSP (*)          |      | 2    |      | Cycle | Guarantee by Design |

#### **Timer Section:**

| Parameter                      | Symbol              | Min. | Тур. | Max. | Unit | Conditions    |

|--------------------------------|---------------------|------|------|------|------|---------------|

| Burst Mode Frequency           | F <sub>Burst</sub>  | 20   | 22.5 | 28   | KHz  |               |

| PWM Mode Frequency             | F <sub>PWM</sub>    | 95   | 100  | 105  | KHz  |               |

| Voltage stability of Frequency | F <sub>PSRR</sub>   | -1   |      | +1   | %    | VDD = 11V~25V |

| Frequency Shuffling Range      | F <sub>jitter</sub> | +/-4 | +/-6 | +/-8 | %    |               |

| Maximum duty cycle             | D <sub>MAX</sub>    | 75   | 80   | 85   | %    |               |

| Internal Soft Startup Time     | T <sub>SS</sub>     | 6.7  | 8.6  | 10.5 | mS   |               |

On chip OTP:

| Parameter | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|-----------|--------|------|------|------|------|------------|

| OTP Level |        |      | 150  |      | °C   |            |

| OTP exit  |        |      | 120  |      | °C   |            |

# 650V MOSFET (Drain Pin):

| Parameter                                   | Symbol              | Test Conditions | Min. | Тур. | Max. | Unit | Remark    | Package |

|---------------------------------------------|---------------------|-----------------|------|------|------|------|-----------|---------|

| MOSFET<br>Drain-source<br>Breakdown Voltage | BV <sub>DSS</sub>   | VGS=0V ID=250uA | 650  |      |      | V    |           |         |

|                                             | RDS <sub>(on)</sub> | VGS=10V ID=0.4A |      | 14   | 17   | Ω    | EST.3010M | DIP-7   |

|                                             |                     | VGS=10V ID=0.5A |      | 9    | 12   | Ω    | EST.3012M | DIP-7   |

| Static drain-source<br>on-resistance        |                     | VGS=10V ID=1A   |      | 4.5  | 5    | Ω    | EST.3016M | DIP-7   |

|                                             |                     | VGS=10V ID=1.5A |      | 3.1  | 3.9  | Ω    | EST.3018M | DIP-7   |

|                                             |                     | VGS=10V ID=2.0A |      | 2.2  | 2.6  | Ω    | EST.3020M | DIP-7   |

## 700V MOSFET (Drain Pin):

| Parameter                                   | Symbol              | Test Conditions  | Min. | Тур. | Max. | Unit | Remark    | Package |

|---------------------------------------------|---------------------|------------------|------|------|------|------|-----------|---------|

| MOSFET<br>Drain-source<br>Breakdown Voltage | BV <sub>DSS</sub>   | VGS=0V ID=250uA  | 700  |      |      | V    |           |         |

| Static drain-source<br>on-resistance        | RDS <sub>(on)</sub> | VGS=10V ID=0.45A |      | 12.5 | 15   | Ω    | EST.3021M | DIP-7   |

|                                             |                     | VGS=10V ID=1.0A  |      | 5.5  | 6.5  | Ω    | EST.3025M | DIP-7   |

|                                             |                     | VGS=10V ID=1.25A |      | 4.0  | 5.0  | Ω    | EST.3026M | DIP-7   |

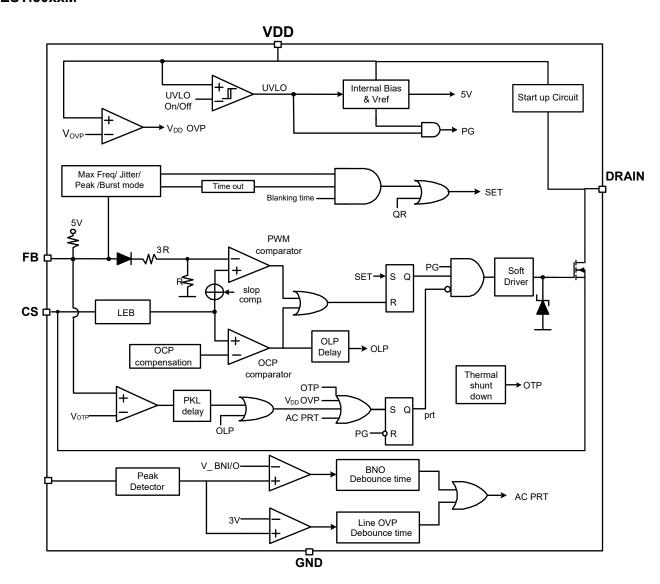

## **Block Diagram**

#### EST.30xxM

#### **Application Note**

#### **Operation Overview**

The EST.30xxM meets the green power requirement and is very suitable for the application of those networking adaptors and the kinds of consumer power. It can provide more power efficiency conversion and keeps lower power loss. It also supports completely kind of protection for every abnormal environments.

#### SS, Soft-start Sequence

EST.30xxM also builds up 8.6 ms (typical) soft-start to soften the electrical stress occurring in the power supply during startup, refer to Fig.2-3. As soon as VDD reaches UVLO \_on, the Cs peak voltage is gradually increased from 0.2V to the maximum level.

Fig.2-3

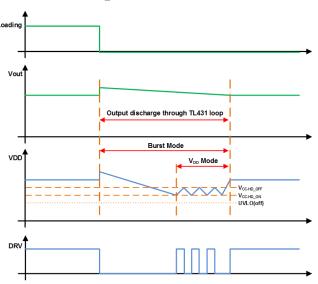

#### **VDD Stimulation Mode**

EST.30xxM provides stimulation mode to avoid abnormal re-start-up under the situation of heavy

loading to no-load, caused by non-balance of discharge of VDD cap and output cap, which is different with burst mode. The waveform is shown in fig.2-4

Condition :  $V_{FB} < V_{BUR\_ON} \& V_{DD} < 9.5V$  trigger, Hysterics Voltage 1V

Action : IC fix output  $F_{Burst}$ , and  $V_{CS}$  keeps as 0.15V

Notice: Design V <sub>AUX</sub> higher than 11V

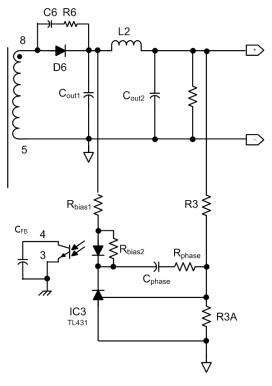

#### FB, Voltage Feedback Loop

EST.30xxM uses current mode control, that is say, the voltage feedback signal is provided from EST.TL431 at secondary side through the photo-coupler to FB pin and compare to the current signal sensing from Cs pin at primary side of MOS current to control the on/off of MOSFET.

In order to enhance light load efficiency, the loss of the feedback resistor in parallel with photo-coupler is reduced. Due to small feedback resistor current, shunt regulator selection and minimum regulation current design have to considered more carefully to make sure it's able to regulate under low cathode current.

To make sure the stability of feedback is very important. Unstable feedback signal will introduce output oscillate or audio noise. You can monitor the ripple & Noise of output to adjust the phase and gain margin of close loop.

(1).  $R_{bias1}$  and  $R_{bias2}$  to prevent the abnormal output

http://www.sthome.com - 7 - Datasheet Rev. 1.0

voltage at heavy loading. Generally, we suggest Rbias1 100~1K $\Omega$ , R<sub>bias2</sub> 1.5~2.5K $\Omega$

- (2). R<sub>phase</sub>/C<sub>phase</sub> is for RC phase compensation and prevent oscillate to adjust the value of CFB

- (3). Generally, we suggest  $R_{\text{phase}}1\text{--}10\text{K}\Omega$  ,  $C_{\text{phase}}$ 0.1uF , C<sub>FB</sub> 1~2.2nF

- (3). The ratio of  $R_3$  and  $R_{3A}$  is depent on the output voltage spec (EST.431, V= 2.5V)

Fig.2-6

In addition, V<sub>FB</sub> is also used to determine the green mode level . When  $V_{FB}$  is under  $V_{BUR\ ON}$  , it is under no load or light load condition; at light loading, burst mode can effectively reduces the switching loss. When V<sub>FB</sub> is larger than V<sub>BUR\_ON</sub>, it will leave away the standby mode. The normal operation of V<sub>FB</sub> is from V<sub>BUR ON</sub> to 2.4V,; meanwhile, short-circuit current is around Izero.

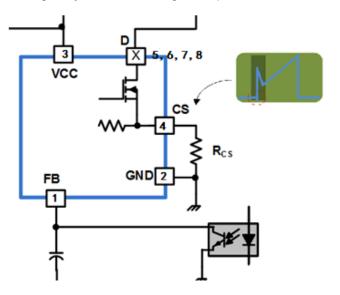

#### CS, Current sense Loop

Current mode PWM control mode detects the current command (CS) from the Rsense (the primary MOSFET current sense resistor) and voltage command from photocoupler (FB) to determine whether the system reaches a stable or not. There is a potential risk of sub-harmonic when the duty of flyback methodology is larger than 50% and the operation under continues conduction mode (CCM), therefore, EST.30xxM also builds in the slope

compensation between high and low AC line to avoid the sub-harmonic risk.

A leading-edge blanking (LEB) time is included in the input of CS pin to prevent the false-trigger from the current spike. Meanwhile, it is strongly recommended to put a suitable R-C filter for higher power application to prevent the CS pin being damaged by the unknow negative spike.

Fig.2-7

#### **Complete Protection**

EST.30xxM integrates various kind of protection to make sure operation safety.

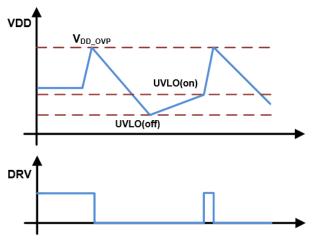

#### **VDD OVP (Over Voltage Protection)**

The maximum ratings of the EST.30xxM are around 30V. To prevent the VDD enter breakdown condition, EST.30xxMS series are integrated with OVP function on VDD pin. Whenever the VDD voltage is higher than the V<sub>OVP</sub> threshold, the output gate drive circuit will be turn-off simultaneously and the power MOSFET is turn-off until the next UVLO(on) cycle.

EST.30xxM

Green-Mode PWM Flvback (SSR)

## **Green-Mode PWM Flyback (SSR)** Controller

Fig.2-8

SDSP, Secondary Diode Short Protection

After short circuit of 2nd side schottky, the inductance current is too low to discharge completely caused by lower output voltage, and then it will continues to increasing to induce abnormal saturation of transformer during LEB timing, therefore, higher peak current induce serious high Vds to damage MOSFET.

EST.30xxM detects the inductance current through the resistance, Rcs, of CS pin, and will trigger protection (latch or hiccup) when Vcs higher than 0.85V and sustains 2cycle timing.

#### Layout Guide line

Better layout plan can reduce unknow noise no matter signal or EMI, please refer to the list below:

Big current path: A&B (Area 1) area are high frequency current loop, line to line is as close as possible, and avoid near low voltage control area

Low voltage area: R devider need to be as near FB\_Pin as possible.

Secondary Side Schottky: routing as close as

Grounding: (2) and (3) grounding separated with each other, and end connects to (1) ground.

# EST.30xxM

# **Green-Mode PWM Flyback (SSR) Controller**

## **Table 1: Complete Protection**

| Issue | Protection |                         | Pin | Protection Conditions                                                   |  |

|-------|------------|-------------------------|-----|-------------------------------------------------------------------------|--|

| 1st   | V-Sense    | VDD OVP                 | VDD | VDD > 26V                                                               |  |

| 1st   | V-Sense    | VDD UVLO Off            | VDD | VDD < 7.5V                                                              |  |

| 1st   | V-Sense    | CS pin open             | CS  | V <sub>CS</sub> > 0.7V after 4 cycles                                   |  |

| 2nd   | SDSP       | 2nd side Schottky short | CS  | VCS > 0.85V after 2 cycles                                              |  |

| 2nd   | SCP        | Output short            | CS  | 1. 12ms blank time during start-up<br>2. after 4 cycles<br>3.Duty < 10% |  |

| 2nd   | OVP        | Output OVP              | CS  | Vcs compares to 0.5V through the resistance divider                     |  |

| 1nd   | OCP        | ОСР                     | CS  | Hi/Low line OCP external adjust , Max current limit CS=0.7V             |  |

| 2nd   | OLP        | OLP                     | FB  | CS > 4V                                                                 |  |

| IC    | Chip OTP   |                         |     | chip OTP at 150 ℃                                                       |  |

EST.30xxM Green-Mode PWM Flvback (SSR)

# **Green-Mode PWM Flyback (SSR) Controller**

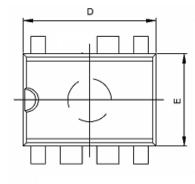

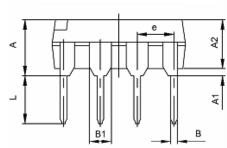

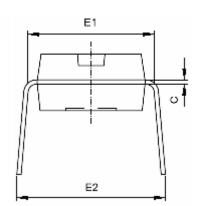

# **Package Information**

# DIP-7 Package ( mm )

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

|        | Min        | Max            | Min                  | Max   |  |

| Α      | 3.710      | 4.310          | 0.146                | 0.170 |  |

| A1     | 0.510      |                | 0.020                |       |  |

| A2     | 3.200      | 3.600          | 0.126                | 0.142 |  |

| В      | 0.360      | 0.560          | 0.014                | 0.022 |  |

| B1     | 1.5        | 24(TYP)        | 0.060(TYP)           |       |  |

| С      | 0.204      | 0.360          | 0.008                | 0.014 |  |

| D      | 9.000      | 9.400          | 0.354                | 0.370 |  |

| E      | 6.200      | 6.600          | 0.244                | 0.260 |  |

| E1     | 7.6        | 20(TYP)        | 0.300(TYP)           |       |  |

| e      | 2.5        | 40(TYP)        | 0.100(TYP)           |       |  |

| L      | 3.000      | 3.600          | 0.118                | 0.142 |  |

| E2     | 8.200      | 9.400          | 0.323                | 0.370 |  |

http://www.sthome.com - 11 -Datasheet Rev. 1.0

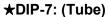

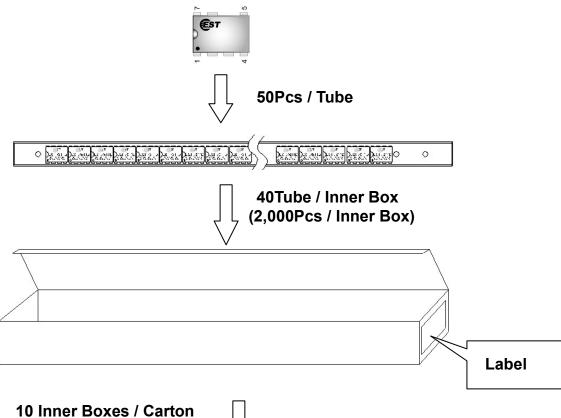

## **Packing Information:**

(10,000Pcs / Carton)

http://www.sthome.com - 12 - Datasheet Rev. 1.0

# EST.30xxM

# **Reliability Test Program**

#### DIP-7

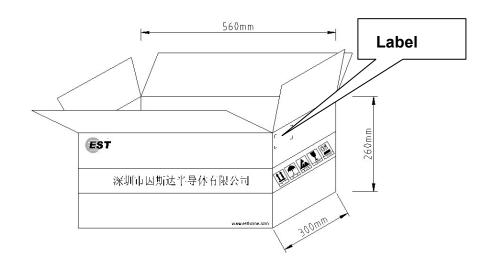

Reflow Condition (IR/Convection or VPR Reflow)

| Test Item     | Method              | Description           |

|---------------|---------------------|-----------------------|

| SOLDERABILITY | MIL-STD-883D-2003   | 245℃, 5sec            |

| HOLT          | MIL-STD-883D-1005.7 | 1000Hrs Bias@125℃     |

| PCT           | JESD-22-B,A102      | 168Hrs, 100% RH, 121℃ |

| TST           | MIL-STD-883D-1011.9 | -65℃~150℃, 200 Cycles |

| ESD           | MIL-STD-883D-3015.7 | VHMB>2KV, VMM>200V    |

| Latch-Up      | JESD 78             | 10ms, 1tr> 100mA      |

http://www.sthome.com - 13 - Datasheet Rev. 1.0

# **Revision History**

| REVISION | DESCRIPTION   | PAGE | DATE       |

|----------|---------------|------|------------|

| Rev 1.0  | First release | 13   | 2020/05/08 |

|          |               |      |            |

|          |               |      |            |

|          |               |      |            |

|          |               |      |            |

|          |               |      |            |

© <a href="http://www.esthome.com">http://www.esthome.com</a>

© 2020 EST Printed in China - All Rights Reserve

http://www.sthome.com - 14 - Datasheet Rev. 1.0